The hard disk drive 100 has disk platters 106, which are driven by motor 108 to rotate as shown. Read and write heads 110 move upon an actuator mechanism 112 driven by a voice coil motor 114. Data detected by the heads is passed through the pre-amp 116 and then a read channel 118 and also used to provide feedback to the head actuator position. This is the driver software used to configure and access a Davong internal hard disk controller for the IBM PC. This controller was significant as being one of the few hard disk systems accessible under DOS 1.x. System instead partitions the disk in to several smaller drives. Diagnostics for the Texas Instruments Professional Computer DOS. Bubble memory is a type of non-volatile computer memory that uses a thin film of a magnetic material to hold small magnetized areas, known as bubbles or domains, each storing one bit of data. The material is arranged to form a series of parallel tracks that the bubbles can move along under the action of an external magnetic field.

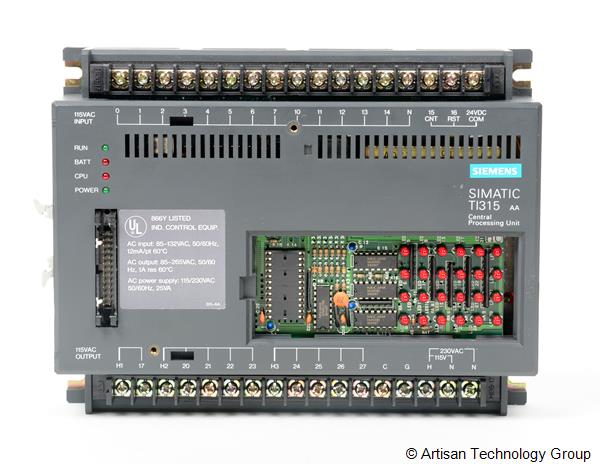

This card was originally developped by Texas Instruments to controlupto three single-density, double-sided drives. One of the drives wasmeantto be installed inside the PE-box, the other two being external, withtheirown power supply. Several other controller cards were developped lateron, to allow for use of double-density disks or even quad-density. Thispage will concentrate on the original TI card, but I will also discussthe FD179x controller used in double-density cards.

The TI controller card consists in: the FD1771 FDC, a 8Kb ROMcontainingthe DSRs and subprograms, and logic circuits to access each of these.TheROM maps at >4000-5FEF, and the FDC registers at >5FF0-5FFF.Thereis also quite a bit of electronics to deal with the drive interface.

Here is an annotated picture of the card.

Theory of operation

Disk physical organisation

Magnetic media and write precomp

Data encoding

Tracks and sectors

CRC

Sector interleaving

Disk logical organisation

Volume information block

File descriptor records

The FDC

FD1771 Pinout

FD179x Pinout

Internal structure

Commands

_Status register

_Stepping commands

__Head-step time

_Read sector

__Sector size codes

_Write sector

_Read ID

_Read track

_Write track

_Force interrupt

The TI controller card

CRU and registers map

Sample programs

Low-level routines

Track-by-track access

Sector access

Checking drive speed

Goofy formats

The card ROM

File buffers in VDP memory

Power-up routine

Device Service Routines

Subprograms

Disk drives

Models

Connection cable

Terminal resistor pack

Shunt pack

Power supply

Theory of operation

Disk physical organisation

Magnetic media

Floppy disks are made of a thin layer of ferromagnetic mediumcoatinga plastic film. Contrarily to paramagnetic or diamagnetic media, aferromagneticelement (or alloy, e.g. iron, cobalt, nickel, Fe65Co35,MnBi, etc) has the property to amplify and possibly to 'remember'an externally applied magnetic field. This is due to the number ofelectronsin the outside layer of ferromagnetic atoms: each atom behaves like atinymagnet. Since magnets attract/repell each other, an atom can recruititsneighbours and force them to point in the same direction than itself.Theseatoms can in turn recruit their neighbours, and the process goes on...until it clashes with another cluster of atoms, oriented differentlyandtoo large to be recruited. A ferromagnetic medium is thus made ofmillionsof tiny domains, into which the atoms are oriented in the samedirection.Each domain acts as a little magnet, but since they are randomlyorientedthe gobal result is magnetically 'neutral'.

However, if an external magnetic field is applied to a ferromagneticmedium, it can force some of the domains to align themselves in thedirectionof the field. The easier domains to recruit will of course be thosewhoseorientation is already close to that of the field. But if the field isstrong enough, and if it lasts long enough, it will eventually recruitall domains. When the field is interrupted the domains remain frozen asthey were, which means that the medium is not globally neutral anymore:it now behaves like a magnet. The intensity of the remaining field withrespect to the field that created it is known as remanence, anddepends on the element/alloy used.

There are two ways to reverse this magnetization: the first one istoapply an external magnetic field with the opposite orientation. Theintensityneeded to cancel a magnetization is known as coercivity. Againitdepends on the type of atom involved: as you may suspect, elements thathave a high remanence also have a high coercivity, they are known asmagneticallyhard elements. The other way to cancel a magnetisation is to warm upthemedium above its 'Curie point': the temperature at which themolecular motion becomes strong enough so that atoms can overcome theirdependance to their neighbours and freely change their orientation(thisproperty is used in magneto-optic disks).

With floppy disks, a magnetic head generates a magnetic field strongenough to magnetize a small area in the ferromagnetic layer of thedisk.Originally some drives used to orient these 'magnets' vertically(i.e whithin the thickness of the layer itself), but nowaday all drivesarrange the magnetic domains horizontally, along the tracks. When thediskmoves, these magnetized area generate a current in the reading head andcan therefore be detected. Note however that only changes inmagneticfields generate current, thus if a disk does not spin it can still bewritten(at the bit currently under the head), but nothing can be read back.

Not all floppy disks are born equal however: high-density disk (HD)are made of a medium with higher remanence and coercivity than single-or double-density disks. This allows to pack bits closer to each other,but requires a writing head capable of generating stonger magneticfields.HD drives can do that, and they can also reduce their write current tohandle SD or DD diks. However, SD or DD drives cannot handle HD disks:their read/write head just can't generate enough magnetic field toovercomethe coercivity of the medium.

A big problem with magnets is that they attract and repell eachother.This is also true for the small magnetic areas used to encode bits!Withcertain bit patterns the attraction/repulsions of several successivebitscombine is such a way that it can result in 'bit shifting', i.e.a bit moves slightly ahead, or behind the positions it should occupy ona track. This is especially marked towards the center of the disk,sincethe inner tracks are shorter but must hold the same amount ofinformationthan the outer tracks: the distance between bits is thus smaller andtheattraction they apply to each other is stronger.

To overcome that phenomenon, that could give rise to readingproblems,some disk controllers use a special trick known as 'writeprecompensation':depending on the bit pattern, critical bits can be written slighltyearlieror slightly later than they should. When shifting occurs, these bitsendup precisely where they are supposed to be. Nifty, isn't it?

Data encoding

Data can be stored on magnetic media using various encoding schemes.The original one was FM (frequency modulation), wich was later modifiedinto MFM (modified frequency modulation). Nowadays, more sophisticatedmethods are used (such as RLL: run length limited), but the TIcontrollercards don't know about them.

FM

In FM, clock bits are recorded at regular intervals. In between twoclock pulses, there can be a data pulse or not. If there is a pulse, itencodes a '1' bit, else it encodes a '0'. This is howa byte (>A3: 10100011) is encoded using FM:

MFM

Things are a tad more complicated with MFM: the data bits areencodedas above, with a pulse for '1' and no pulse for '0'.But clock bits are only issued in between two '0' data bits.Here is how the same byte is encoded with MFM:

As you can see, this method leaves more room between pulses, whichmeansthat we can compress the above by a factor of two and still have thesameminimum interval between pulses than with FM:

Marks

The controller is also able to record some bytes in a special way.These bytes will be used as synchronisation marks, to define thebeginningor the end of a data area for instance.

The way it is done in FM is by omitting two or three clock pulses inthe middle of the byte. We saw above that there are normally 8 clockbitsper byte. If we represent each clock bit with a '1', the normalclock pattern is thus 11111111, or >FF. This clock pattern isinterlacedwith the data bits for synchronisation purposes. The FD179x can encodemarks with a >C7 (11000111) or a >D7 (11010111) clock pattern. Toprevent the controller from completely loosing sync, the bytes encodedwith such a clock pattern should contain a lot of 1s: the FD179x uses>F8-FBor >FE with a >C7 clock pattern, and >FC with a >D7 clockpattern.

In the TI-99/4A disk format described below,a >FE mark signals the ID block in a sector, whereas a >FB marksignalsthe data block. A >F8 indicates a deleted data mark. Finally, theIBMformat uses >FC at the beginning of the track, to mark the locationof the index hole on the track. The unique >D7 clock pattern of the>FC mark tells the CRC logic not to reset the CRC count, as itnormallydoes with sector marks. Track marks are not part of the TI-99/4A format.

Data mark:

ID mark:

Track mark:

In MFM, marks are generated by omiting a clock transition between bits4 and 5, or between bits 3 and 4 of the data byte. Obviously, thesedatabits must be 0s, otherwise no clock bit would be expected there. ThetwoMFM marks are >A1 (missing a clock bit between bits 4 and 5) forsectormarks, and >C2 (missing a clock bit between bits 3 and 4) for trackmarks. An MFM mark is repeted 3 times and followed by a normallyencodedbyte, with the value of the corresponding FM mark (>FB, >FE,>FC,etc). Byte >FC comes after three >C2 track marks, all other bytesafter three >A1 sector marks.

Sector marks

Track mark

Tracks and sectors

A disk is divided into a number of concentric circles called tracks.Each track is in turn divided into several data segments calledsectors.Finally, most floppy disks can be written on both sides.

The number of sides per disk and the number of tracks per sidedependon the hardware: you need two reading heads to access both sides of adisk.And the number and positions of the tracks depends on the mechanicsthatmove the reading head in the drive. Typically, TI-drives have 35 or 40tracks per side. IBM drives can have upto 76 tracks.

On the other hand, the number and the size of the sectors do notdependon the hardware. It is said that floppies are 'soft sectored'(hard-sectored disks have an index hole for each sector, soft-sectoreddisks have only one hole). In the TI single-density format, there are 9sectors per track, each 256 bytes in length. Double-density format has18 sectors per track. But this is no obligation: you could elect tohaveonly one big sector per track : this will result in faster datatransfer,but may cause a tremendous waste of space if your file is just 1 bytelargerthan a sector.

Each sector is composed of two parts: a sector ID block and a datablock.The sector ID block contains the track number, the side, the sectornumberand a code for the sector size. When you access a sector, the FDCcheckseach ID block until it finds one that with the right sector, track andside numbers. If it does not find one after 5 disk revolutions, itreturnsa 'record not found' error. Not surprisingly, the data blockcontains data, to be transfered to or from the CPU. Each block endswitha CRC byte (cyclic redundancy check) which is a way for the FDC toensurethat the information on the disk has not been corrupted. Special marks(recorded in a special way) are used to define the begining of eachblockafter a stretch of zeros intended to allow for synchronisation.

A track begins shortly after the index hole has been detected by thecontroller: there are a few >FF filler bytes before the firstsector.Similarly, any unused space after the last sector is filled by >FFbytes.There are also filler bytes between the ID and data blocks.

Hard Disk Drive Repair

In summary, here is how a single-density track looks like in the TIformat. The part in bold type is rewritten during sector writeoperations.The number of bytes preceded by a ~ may vary when a sector isrewritten,due to slight variations in the speed of the drive motor (especially,ifthe sector was written with another drive than the one used toinitializethe disk).

| Name | Bytes | Value | Description | |

|---|---|---|---|---|

| Index gap | 12 | >FF | Index mark filler | |

| x9 | ID sync | 6 | >00 | Synchronizes the controller for ID mark |

| ID mark | 1 | >FE | Recorded in a special way (clock >C7) | |

| Track | 1 | >00-FF | Track number (normally 0-39) | |

| Side | 1 | >00-01 | >00=side A, >01=side B | |

| Sector | 1 | >00-FF | Sector number (normally 0-8) | |

| Length | 1 | >01-04 | Sector size (normally >01: 256 bytes) | |

| CRC | 2 | crc | Cyclic redundance check | |

| Separator | ~11 | >FF | Prevents 'Write sector' from erasing the ID block | |

| Data sync | 6 | >00 | Synchronizes the controller for data mark | |

| Data mark | 1 | >FB | Recorded in a special way (clock >C7) | |

| Data | 256 | data | This is the data contained in the sector | |

| CRC | 2 | crc | Cyclic redundancy check | |

| Separator | ~36 | >FF | Prevents 'Write sector' from erasing next ID block | |

| End filler | ~240 | >FF | Varies with motor speed (+/- 32 bytes) |

Total data bytes: 9 x 256 = 2304 bytes

Total sector bytes: 9 x 325 = 2925 bytes

Total per track: about 3177 bytes

And here is a double-density track.

| Name | Bytes | Value | Description | |

|---|---|---|---|---|

| Index gap | 32 | >4E | Index mark filler | |

| x18 | ID sync | 12 | >00 | Synchronizes the controller for ID mark |

| MFM mark | 3 | >A1 | Recorded in a special way (missing clock 4-5) | |

| ID mark | 1 | >FE | Recorded in normal MFM | |

| Track | 1 | >00-FF | Track number (normally 0-39) | |

| Side | 1 | >00-01 | >00=side A, >01=side B | |

| Sector | 1 | >00-FF | Sector number (normally 0-17) | |

| Length | 1 | >01 | Sector size (normally >01: 256 bytes) | |

| CRC | 2 | crc | Cyclic redundance check | |

| Separator | ~22 | >4E | Prevents 'Write sector' from erasing the ID block | |

| Data sync | 12 | >00 | Synchronizes the controller for data mark | |

| MFM mark | 3 | >A1 | Recorded in a special way (missing clock 4-5) | |

| Data mark | 1 | >FB | Recorded in normal MFM | |

| Data | 256 | data | This is the data contained in the sector | |

| CRC | 2 | crc | Cyclic redundancy check | |

| Separator | ~28 | >4E | Prevents 'Write sector' from erasing next ID block | |

| End filler | ~190 | >FF | Varies with motor speed: (+/- 32 bytes) |

Total data bytes: 18 x 256 = 4608 bytes

Total sector bytes: 18 x 346 = 6228 bytes

Total per track: about 6450 bytes

Cyclic Redundancy Check

Cyclic redundancy check (CRC) is a very powerfull method to detect adata alteration the disk, or a transmission error. Unfortunately, it'snot as simple to explain as a checksum, but I'll do my best.

We saw above that the data block of a sector is normally 2048-bitlong.Traditionnally, we think of these bits as 256 bytes of 8 bits, butnothingprevents us to consider them as 128 words of 16 bits or even as asingle2048-bit number. The lattest provides us with a nice way to verify dataintegrity: let's just divide this huge number by an arbitrary value andstore the result (the quotient or the remainder) toghether with thedata.The problem with the quotient is that it may well be a very largenumberin itself and may require many bits of storage space. The remainder, onthe other hand, is by definition smaller than the divisor by at least 1bit. Therefore, if we were to use a 17-bit divisor, we would be sure toget a 16-bit remainder that can conveniently be stored as two extrabytes,toghether with the sector data. It's not completely impossible that analteration of the data will result in a number that provides the sameremainder,but it's very unlikely: for a 16-bit remainder (17-bit divisor) theoddsare 1/216, i.e. one chance in 65536.

The only problem with this technique is that long divisions aredifficultto perform for electronic circuits. For neuronal circuits also: justtryto divide 12,146,753,456 by 1,247. You have five seconds.Answer......now!

One way to make it easier is to split the operation into a series ofpartial divisions, and to combine them with shifts and substratctions.This is the traditional way we learn at school:

We could to the same with binary numbers. It would even be easiersincethere are only two posible answers to the question 'how many timesX in Y?', these are 0 and 1. Thus we can replace partial divisionswith comparisons: 'is X greater than Y?', which is much easierto perform for electronic circuits. What's less easy to obtain is theremaindersince substactions (and additions for that matter) require moderatelycomplicatedcircuits, due to the need to borrow (or carry) bits from the nextpositionon the left. Things would be easier if we could replace substractionswitha bitwise operation such as AND, OR or XOR.

But wait, nothing prevents us from doing it! The result may not beverymeaningfull, but as long as it retains the same properties than adivisionthat's all we need. CRC codes are generated with such'pseudo-divisions',that use an XOR operation instead of a substraction. Just to refreshyoumemory: a XOR operation on two bits results in 1 when one or the otherbit is 1 (but not both). The truth table is:

Now let's 'divide' 111001 by 1101 (both being binary values:57 and 11 in decimal) using our XOR-division scheme:

As you see, this kind of operation is fairly easy to perform for ahumanbrain, and even more so for an electronic circuit. The final'remainder'is our CRC value. Just like the remainder of a division, it is notuniqueto a given dividend, but the probability that an altered dividend givesthe same CRC than the original one is very low. More precisely it is 1/2n, where n is the number of bits in the CRC value.

This means that our 16-bit CRC scheme will pick up 65535 errors outof 65536, or 99.9985 %. Not bad, eh? But we can make it even better ifwe consider the way errors appear on a disk. They can be due tospontaneousdemagnetisation, in which cas only one or two bits at a time will beaffected,unless you let a disk sit for 10 years. Or a precise spot on the diskmaybe damaged and the faulty bits will be grouped toghether (at the placeyou put your greasy fingers on the magnetic medium). So is often thecasewith serial transmissions: a burst of statics scrambles a whole bunchofbits. It turns out that some CRC 'divisors' (the official nameis 'generator') are better than other at detecting such bursterrors. For instance, the widely-used CCITT generator1,0001,0000,0010,0001results in the following impressive performances:

| Type of error | Detection rate |

|---|---|

| Single bit errors | 100% |

| Two bits errors | 100% |

| Any even number of faulty bits | 100% |

| Burst errors of 16 bits or less | 100% |

| Burst errors of 17 bits | 99.9969% |

| All other burst errors | 99.9984% |

This happens to be the CRC generator used by the FD197x controller.

By the way, did you notice that it's not very convenient to 'spellout' a generator, even if we use comma to group the bits 4 by 4?Therefore,the traditional way of writing down a CRC generator is to give itspolynomial,i.e. which of the bits are set to 1. In the case of the CCITTgenerator,the polynomial is x16+x12+x5+1, i.e.bits16, 12, 5 and 0 (x0 =1) are set to 1. For obvious reasonstheleftmost bit is always 1 in CRC generators (otherwise we would have15-bitCRC values and lower error detection rates). For reasons that are muchless obvious to me, the rightmost bit should also be 1.

One last detail. You may think that when reading data from the disk,the controller calculates the CRC and compares it with the CRC valuewrittenon disk. You're close, but no cigar. You see, this would require aspecialcomparison circuit. On the other hand, one can check if two numbers areidentical by XORing them: A xor B is always 0 if, and only if, A=B. Itis thus possible to use the existing XOR logic in the CRC circuitery toperform the check. This is done as follow:

When writing a sector, the FDC considers it as a 2064-bit number,madeof 256 8-bit bytes plus a trailing >0000 16-bit word. Upon writing,it replaces the final >0000 with the CRC value. When reading, itjustcalculate the CRC of the 2064 bits: the result should be 0 since theCRCvalue will be XORed with itself.

This may remind you of the method used to check parity in serialtransmission chips. No wonder: the parity bit is nothing else thana 1-bit CRC. Odd parity uses a 10 generator, and even parity a 11generator(i.e. the polynomial is x+1). Of course, the error detection rate isfairlylow since 1/21 is only 50%...

Sector interleaving

A word about numbering. On each side tracks are numbered from 0 to39starting from the outside of the disk. On each track, sectors arenumberdfrom 0 to 8 (or to 17 for DD disks). When you try to a sector, thesoftwaredetermines on which track it is, and what sector number is will have onthis track. Note that sector numbers grow inwards on side A, butoutwardson side B (even though track numbers grow inwards on both sides).

However, this numbering scheme is only a software convention, youareallowed to use another numbering scheme provided your software knowshowto deal with it. For instance, some protection programs assign randomnumbersto their sectors (41, 12, 88, 26, etc). The loading software knowswhichsector to call on which track, but plain-vanilla disk managementsoftwaresare completely lost and cannot copy such a disk (see goofyformats, below).

Even though sectors are numbered from 0 to 8, they need not to bearrangedin this order on the track. In fact, it is generally better that theyarenot! This is because it will take some time for the software to dealwitha sector before trying to access the next one. In the mean time, thediskwill have spun and may have skipped several sectors. To optimize accessspeed, it is thus advisable to figure out an interleaving (a.k.a.interlacing)scheme designed in such a way that reading head arrives on the nextsectorjust when the software is ready to access it.

For instance, assume that the disk spins by three sectors before thesoftware is ready to proceed. The ideal sequence of sectors would besomethinglike this: 0 x x x 1 x x x 2 x x x 3 x x x 4 x x x 5 x x x 6 x x x 7 xx x 8. Since tracks are circular, this sequence results in thefollowinginterleave: 0 7 5 3 1 8 6 4 2. You can verify that consecutive sectorsare always 4 sectors apart on the disk (this happens to be the bestinterlacepattern for the TI disk controller card).

Disk logical organisation

Volume information block

The first two sectors on the disk are reserved for importantinformationabout the disk and its content. One uses the first sectors because theyare on the outside of the disk, where tracks are physically longer thanin the center. Since floppies rotate at a constant speed (unlike CDs),there will be more space to write the same amount of information ontrack0 than on track 39. As a result, the probability of data corruption isless on the outer tracks.

Sector 0

This sector is called the VIB (volume information block) andcontainsvarious information about the disk: name, size, protection, and mostimportantlya sector bitmap.

This bitmap is used by the software to determine whether a sector isfree or used. Each sector is represented by one bit (starting with theleast significant bit of each byte): when the bit is 0, the sector isfreeand can be used to create a new file or appended to an existing file.Whenthe bit is 1, the sector is either used or damaged. There are 200 bytesavailable in the bitmap, which is enough to map 1600 sectors. That'smorethan enough, since even DS/DD disks have only 1440 sectors.

Content of sector 0:

| Bytes | Contents | Typical values |

|---|---|---|

| >00-09 | Disk name | 'DISKNAME01' |

| >0A-0B | # of sectors | SS/SD: >168 DS/SD: >2D0 SS/DD: >2D0 DS/DD: >5A9 |

| >0C | Sectors/track | SD: >09 DD: >12 |

| >0D-0F | DSR mark | 'DSK' |

| >10 | Protection | Unprot: ' ' Protected: 'P' |

| >11 | Tracks/side | >23 / >28 |

| >12 | Sides | >01 / >02 |

| >13 | Density | SS: >01 DS: >02 |

| >14-37 | (reserved) | >00 |

| >38-EB | Bitmap | SS/SD: >38-64 DS/SD and SS/DD: >38-91 DS/DD: >38-EB |

| >EC-FF | (reserved) | Must be >FF |

Some reserved bytes are sometimes used by disk managers to storeextrainformation about the disk: for instance, DISKU by the late JohnBirdwellstores an 8-char date string into bytes >20 to >27.

Sector 1

This sector contains a list of pointers (i.e. sector numbers) tofiledescriptor records, sorted in alphabetical order. Each pointer is 2byteslong (since there are more that 256 sectors on a disk) and the listendswith >0000, which allows us to list 127 files per disk.

Interesting things happen when you play around with that sector:

File descriptor record

Each file consists of at least one sector, even when empty. Thissectoris known as the File Descriptor Record (FDR) and contains variousinformationsabout the file: its name, its type, its size, etc. It also contains alistof the sectors where the file data is to be found. The list does notenumerateeach sector as this would drastically limitate the maximum file size.Ratherit lists clusters, i.e. chunks of consecutive sectors belonging to thefile.

Ideally, a file should consist in only one big cluster. However, asother files are written on the disk, it may be that the next sector isnot available when it is time to increase the file size. It is thusnecessaryto start a new cluster, in a free area of the disk: the file is nowfractured.Disks that contain a lot of files that have often been modified mayend-upin a awfully fractured way, which results in decreasing the accessspeed(as the reading head must move from one cluster to the next) and mayimposea limit on the file size (as only 76 clusters can be defined in theFDR).Therefore, most disk managers will rearrange the files in singleclusterswhen copying a disk.

The FDR dedicates three bytes per cluster, that are used to definethesector number where the cluster begins and the total file size (insectors,minus one) reached with this cluster. As both numbers may be biggerthan256, each is encoded using one byte and a half (3 nibbles), as follow:UM SN OF Where N U M are the three nibbles forming the sector number(inthis order) and O F S are the three nibbles forming the total fileoffset(counting from zero).

Exemple:

A file consists in 7 sectors: sectors >02E and >02EF andsectors>192-196 (5 more sectors).

This makes two clusters: the first starts at sector >02E and endswithan offset of >001, the second starts at sector >192 and ends witha total of >006 sectors.

The cluster list would thus look like this: >2E >10 >00 >92>61 >00.

Note: the DISKU disk manager uses the end of the FDR to store a userdefined comment about the content of the file, in bytes 220 to 254. IsupposeJohn Birdwell assumed no file will be so hopelessly fractured as torequiremore that 64 clusters...

| Bytes | Contents | Comments |

|---|---|---|

| >00-09 | File name | 'MYFILE01' |

| >0A-0B | (reserved) | >00 |

| >0C | File type | >80: variable >08: write protected >02: internal >01: program |

| >0D | Records/sector | >00 for program files |

| >0E-0F | # of sectors in file | Not counting FDR |

| >10 | Last byte in last sector | >00 for fixed files |

| >11 | Record length | >00 for program files |

| >12-13 | Fixed: number of records Var: number of sectors Program: >00 | ! Bytes are swapped ! |

| >14-1B | (reserved) | >00 |

| >1C-FF | Cluster list | >UM >SN >OF >NUM >OFS |

The FD1771 Floppy disk controller

The Floppy Disk Controller (FDC) is the microprocessor that carriesout all disk operations: it starts and stops the motor, moves thereadinghead to the required track, searches for the specified sector, andreadsor writes it one bit at a time. It transfers these bits to/from the CPUone byte at a time.

The FD1771 encodes data in FM (frequency modulation) and canthereforeonly handle single-density disks.

Pinout

Power supply

Vdd: +12 Volts

Vcc: +5 Volts

Vbb: -5 Volts

Vss: Ground

Computer interface

MR*: Master Reset. When hold low for at least 50 usec, thisinput pin resets the FDC and resets the 'Not-ready' status bit.When MR* becomes high again, the FDC executes a Restore (>03)commandand loads >01 into the Sector register.

CS*: Chip Select. Enables FDC access when low.

A0,A1: Address lines. Select the register to be accessed.0=Command(write) or Status (read), 1= Track, 2=Sector, 3=Data.

DAL0-DAL7: Data Access Lines. Inverted bidirectional data bus,enabledby WE* and RE*.

WE*: Write Enable. Used by the CPU to tell the FDC that data hasbeen sent on the data bus. Active low.

RE*: Read Enable. Used by the CPU to read cause the FDC to placedata on the data bus. Active low.

CLOCK: This input pin must receive a 2 MHz +/- 1% square wavesignal,with a 50% duty cycle.

DRQ: Data Request. This open collector output is used by the FDCduring read operations to indicate that a byte of data is ready in theData register (high signal). During write operations, a high levelsignalsthat the Data register is now empty and ready to receive another byte.Should be pulled up to +5V with a 10K resistor.

INTRQ: Interrupt request. This open collector output (to bepulledup with a 10K to +5V) becomes low each time the FDC has completed acommand.Reset when the command register is loaded with a new command.

Disk drive interface

The FD1771 can be handle two types of drive interface: it caneithercommand 3 stepper motors by sending successive three phase pulses onpinsPH1, PH2 and PH3, or it can send stepping pulses on the PH1/STEP pinanda direction control on the PH2/DIRC pin. Pin 3PM is used to determinethetype of interface used.

PH1*/STEP: If 3PM is high. the FDC sends a 4 microsecondshighpulse on this output pin, causing the drive to move the reading head byone track. If 3PM is low, the FDC sends one active low signal out ofthreeon this pin.

PH2*/DIRC: When 3PM is high, this pin determines the directioninwhich the head will move. Low=outwards, high=inwards. If 3PM is low,theFDC send one active low signal out of three on this pin.

PH3: When 3PM is low, the FDC sends one active low signal out ofthree on this pin. Not used if 3PM is high. Note that PH3 needs anexternalinverter.

3PM: This pin should be hardwired low to use a 3-step driveinterface:pulses will be sent as PH1-PH2-PH3-PH1 to step in and asPH1-PH3-PH2-PH1to step out. Alternatively, 3PM can be wired high for a moresophisticatedinterface: a single stepping pulse will be sent on STEP. whith DIRCindicatingthe direction.

TG43: Track greater than 43. This output pin tells the drivethatthe head is positioned beyond track 43 (some drives use it tocompensatefor the higher density of data bits on these tracks). Valid only duringread and write commands.

HLT: Head Loading Time. When high, the magnetic head is assumedto be engaged. This input is typically driven by a one-shot timertriggeredby HLD but could also be connected to +5V if the internal delay issufficient(command bit 'E': the HLT line will only be sampled 10 ms afterHLD went high).

HLD: Head load. Tells the drive to load the read/write head onthemagnetic medium. Typically used to trigger a one-shot that fires backtoHLT.

The FD1771 can either receive a mixed signal from the drive, i.eclockand data bits together, or receive the clock bits on pin FDCLK and thedata bits on pin FDDATA. Pin XTDS is hardwired to determine the mode tobe used.

FDCLK: When XTDS* is low, this pin receives the clock bitsfromthe drive, processed by an external separator. If XTDS* is low, thispinshould be tied to a logic high.

FDDATA: Data input from the drive. When XTDS* is low, this pinreceivesexternally separated data bits from the drive. If XTDS* is high, thispinreceives raw data from the drive and an internal separator is used.

XTDS*: This pin should be hardwired low if an external dataseparatoris used. It should be tied high or left open to make use of theinternaldata separator.

WG: Write Gate. Becomes active before write operations.

WD: Write Data. This output pin sends 500 ns pulses to the drivefor each flux transition. This signal always incorporates data andclockbits (including marks), no matter the status of XTDS*.

READY: Input pin used by the drive to tell the FDC that it isreadyfor the next operation.

WF*: Write fault. The drive can bring this pin low to indicatewrintingfaults. If WG was high, the current write command is terminated and the'write fault' status bit is set. This line should remain inactive(high) when WG is low.

TR00*: Track 0. The drive uses this pin to inform the FDC thatthehead is on track 0 (to the outside of the disk). Active low..

IP*: Index pulse. Used by the drive to signal index holes.Low=hole.

WPRT*. Write protected. Used by the drive to signal a writeprotection.A low level aborts any write command and sets the 'write protected'status bit.

DINT*: Disk Init. Used to prevent disk formating: the FD1771samplesthis input when a Write Track command is received. If the pin is low,theoperation is terminated and the 'write protected' status bitis set.

TEST*: Ouput pin for test purposes. Should be left open orpulledup to +5V.

The FD179x-02 Floppy disk controller

The Floppy Disk Controller (FDC) is the new version of the FD1771.Themain improvement is that it can handle double-density disks, byperformingMFM encoding.

There are six, slightly different FD179x models. The FD1791, FD1792and FD1795 have an inverted data bus. The FD1791, FD1793, FD1795 andFD1797can deal with double-density. The FD1795 and FD1797 have a sideselectionoutput.

Pinout

Power supply

Vdd: +12 Volts

Vcc: +5 Volts

Vss: Ground

Computer interface

MR*: Master Reset. When hold low for at least 50 usec, thisinput pin resets the FDC and resets the 'Not-ready' status bit.When MR* becomes high again, the FDC executes a Restore (>03)commandand loads >01 into the Sector register.

CS*: Chip Select. Enables FDC access when low.

A0,A1: Address lines. Select the register to be accessed.0=Command(write) or Status (read), 1= Track, 2=Sector, 3=Data.

DAL0-DAL7: Data Access Lines. Bidirectional data bus. Invertedonthe FD1791, FD1792 and FD1795.

WE*: Write Enable. Used by the CPU to tell the FDC that data hasbeen sent on the data bus (pins DAL0-DAL7).

RE*: Read Enable. Used by the CPU to read cause the FDC to placedata on the data bus.

CLOCK: This input pin must receive a 1 MHz (2 MHz for 8'floppies) square wave signal, with a 50% duty cycle.

DRQ: Data Request. This open collector output is used by the FDCduring read operations to indicate that a byte of data is ready in theData register (high signal). During write operations, a high levelsignalsthat the Data register is now empty and ready to receive another byte.Should be pulled up to +5V with a 10K resistor.

INTRQ: Interrupt request. This open collector output (to bepulledup with a 10K to +5V) becomes low each time the FDC has completed acommand.

Disk drive interface

STEP: The FDC sends a pulse on this output pin, causing thedrive to move the reading head by one track.

DIRC: Direction. This output pin determines in which directionthehead will move. Low=outwards, high=inwards.

TG43: Track greater than 43. This output pin tells the drivethatthe head is positioned beyond track 43. Valid only during read andwritecommands.

HLT: Head Loading Time. When high, the magnetic head is assumedto be engaged. This input is typically driven by a one-shot timertriggeredby HLD but could also be connected to +5V if an internal delay is used(command bit 'E')..

HLD: Head load. Tells the drive to load the read/write head onthemagnetic medium. Typically used to trigger a one-shot.

SSO: Side Select Ouput. Tells the drive which side of the disktoaccess (for FD1795/97 only).

RG: Read Gate. Used for synchronisation of external dataseparators(for FD1791-94 only). Goes high after two >00 bytes in SD (4 bytesof>00 or >FF in DD).

DDEN*. Double Density Enable. This input pin puts the FDC indouble-densitymode when low, in single-density mode when high. Must be left open ontheFD1792/1794 (that cannot handle double density).

EARLY: When active (high) indicates that the write data pulseshouldbe shifted early for write precompensation.

LATE: When active (high) indicates that the write data pulseshouldbe shifted early for write precompensation.

RCLK: Read Clock. The drive sends a nominal square wavesignalderived from the data stream on this pin. The polarity of the signal(+/-)does not matter, only phasing (i.e. transitions) does.

RAWREAD*: Data input from the drive. Active low, i.e. eachrecordedflux transition should send a negative pulse.

WG: Write Gate. Becomes active before write operations.

WD: Write Data. This output pin sends a 500 ns (FM) or 200 ns(MFM)pulse to the drive for each flux transition. This signal incorporatesdataand clock bits (including marks).

READY: Input pin used by the drive to tell the FDC that it isreadyfor the next operation.

WF*/VFOE*: Compined input/output pin. During write operations(whenWG is high) this pin is used as input for a Write Fault signal: whenactive(low) it interrupts the current write command. During read operations(whenWG is low) this pin becomes a VFO enable output signal.On the FD1791/93it goes low once the head has settled (HLT is high) and remains lowuntilthe end of the data field. Additionally, on the FD1795/97 ittemporarilygoes high between the end of the ID CRC and 4 bytes (8 in MFM) beforethedata mark. This pin has an internal 100K pull-up resistor.

TR00: Track 0. The drive uses this pin to inform the FDC thatthehead is on track 0 (to the outside of the disk).

IP*: Index pulse. Used by the drive to signal index holes.Low=hole.

WPRT*. Write protected. Used by the drive to signal a writeprotection.A low level aborts any write command.

TEST*: Ouput pin for test purposes. Should be left open orpulledup to +5V. Used with voice-coil actuated steppers (i.e. linear steppermotors. But appart for some antiques, all drives use rotating steppermotorsto move the read/write head).

Internal structure

The FDC contains five 1-byte registers: a write-only Commandregister,a read-only Status register, a Data register, a Track register and aSectorregister. These registers are mapped at addresses >5FF0-5FFE in theTI controller card.

The write-only Command register accepts 11 differentcommandsfrom the CPU. They are described below.

The meaning of the various bits in the read-only Status registerdepends on the current command. Several bits reflect the state ofoutputpins ('Busy' for INTREQ, 'DRQ pin' for DRQ, etc), whichgives the designer the option to physically tie those pin to the CPU,orto read them via the Status register. See 'Commands'for more details.

The Data register is used as a holding register during readorwrite operations. It communicates with an internal shift registerthat allows to serialize data to send it to the drive (on the WD pin).Conversely, during read operations, the shift registers accepts datafromthe drive (on the RAWREAD* or FDDATA pin), assembles it into a byte andtransfers this byte to the data register.

The Track register contains the number of the track themagneticread/write head is on. Valid values are 0 to 255, although I don'tthinkany TI-99/4A-compatible drive ever went beyond 76 tracks. The FDCautomaticallyupdates the Track register when stepping the magnetic head. The contentof this register is compared to the track number recorded on the diskduringread, write and verify operations. The track register can also bemodifieddirectly by the CPU.

The Sector register holds the number of the desired sector,asloaded by the CPU. The content of this register is compared to thesectornumber recorded on the disk during read, write and verify operations.

In addition to these five register (and the shift register), the FDCalso contains several functional units that are not directly accessibleby the CPU:

An ALU (Arithmetic and Logic Unit) used to perform comparisonsandregister modifications.

An address mark detector, that checks the clock pulses anddetectsthe ID and data marks.

A CRC logic (Cyclic Redundancy Check), used to write and verifya CRC code on disk. The polynomial is x16+x12+x5+1,which is the standard CCITT CRC generator (see above).

And last but not least, a timing and control circuit, triggeredby an external clock signal, that controls all drive operations.

Commands

The FDC accepts 11 different commands. Their syntax is summarized inthe table below. Be aware that there are subtle differences between theFD1771 and the newer FD179x. Furthermore, there are differences betweenthe various subtypes of FD179x.

Most commands will abort if the drive is not ready: the FDC checksforthat by sampling the READY pin at the beginning of the command. Themeaningof the various bits in the Status register depends on the command beingexecuted, but one constant is the Busy bit (weight >01). No newcommandshould be sent to the Command register as long as this bit is set(apartfor the 'Force interrupt' command). Once the command has beencompleted, the Busy bit is cleared and an interrupt is issued on theINTREQpin.

| Command | >80 | >40 | >20 | >10 | >08 | >04 | >02 | >01 |

|---|---|---|---|---|---|---|---|---|

| Restore | 0 | 0 | 0 | 0 | h | V | r1 | r0 |

| Seek | 0 | 0 | 0 | 1 | h | V | r1 | r0 |

| Step | 0 | 0 | 1 | T | h | V | r1 | r0 |

| Step-in | 0 | 1 | 0 | T | h | V | r1 | r0 |

| Step-out | 0 | 1 | 1 | T | h | V | r1 | r0 |

| Read sector | 1 | 0 | 0 | m | S | E | C/0 | 0 |

| Write sector | 1 | 0 | 1 | m | S | E | C/a1 | a0 |

| Read ID | 1 | 1 | 0 | 0 | 0 | E' | 0 | 0 |

| Read track | 1 | 1 | 1 | 0 | 0 | E' | 0 | s* |

| Write track | 1 | 1 | 1 | 1 | 0 | E' | 0 | 0 |

| Force interrupt | 1 | 1 | 0 | 1 | I3 | I2 | I1 | I0 |

r0,r1: stepping motor rate (see below)

V: verify track number flag. 1=verify, 0=don't.

h: head load flag. 0=unload head at beginning, 1=load head atbeginning.

T: track update flag. 1=update track register, 0=don't.

a0: data mark flag. For FD179x: 0=data mark (>FB),1=deleteddata mark (>F8). For FD1771: combined with C to select one in 4possibledata marks: 00 = >FB, 01 = FA, 10 = >F9, 11 = >F8.

E: delay flag: 0=no delay, 1=15 msec delay before sampling theHLTpin (10 msec for FD1771).

E': same as E, but always 1 with FD1771.

C/a1: For FD1795/97: compare side number flag. 0=disable,1=enable:set value of SSO pin (for all read/write commands). For the FD1771:always0 for read command, combines with a0 for write commands.

S: For FD 1791/2/3: expected side, to be compared to side numberon disk if C=1. For FD1771 and FD1795/97: changes the meaning of the sectorsize code.

m: multiple record flag. 0=read/write one sector. 1=keepreading/writingsectors on that track until Force interrupt is issued.

s*: For FD1771 only. Synchronize to address marks if 0, ignoreaddressmarks if 1. Always enabled with the FD179x.

I3: issue an interrupt now. This bit can only be reset withanother'Force interrupt' command.

I2: issue an interrupt at the next index pulse.

I1: issue an interrupt at the next ready to not-ready transitionof the READY pin.

I0: issue an interrupt at the next not-ready to ready transitionof the READY pin.

(If I0-I3 are 0: don't issue any interrupt, but still abort the currentcommand).

Status register

The meaning of the status bits for the different commands issummarizedbelow:

| Command | >80 | >40 | >20 | >10 | >08 | >04 | >02 | >01 |

|---|---|---|---|---|---|---|---|---|

| All steppings + Force interrupt | Not ready | Write protect | Head loaded | Seek error | (CRC error) | Track 0 | Index pulse | Busy |

| Read ID | Not ready | 0 | 0 | Rec not found | CRC error | Lost data | DRQ pin | Busy |

| Read sector | Not ready | 0 (Mark type) | Mark type | Rec not found | CRC error | Lost data | DRQ pin | Busy |

| Read track | Not ready | 0 | 0 | 0 | 0 | Lost data | DRQ pin | Busy |

| Write sector | Not ready | Write protect | Write fault | Rec not found | CRC error | Lost data | DRQ pin | Busy |

| Write track | Not ready | Write protect | Write fault | 0 | 0 | Lost data | DRQ pin | Busy |

Not-ready: inverted copy of the READY input pin ('ORed'with MasterReset pin). A 1 indicates the drive in not ready.

Write protect: inverted copy of the WPRT* input pin. A 1indicatesthe disk is write protected.

Head loaded: logical 'and' of HLD and HLT pins. A 1 indicatesthe head is loaded and engaged.

Seek error: if 1, the desired track did not match. Reset whenupdated.

CRC error: if 1 the CRC found on disk did not match thecalculatedone. For stepping commands: CRC found in an ID field..

Track 0: inverted copy of the TR00* input pin. A 1 indicates themagnetic head is on track 0.

Index pulse: inverted copy of the IP* pin. A 1 indicates anindexhole.

Busy: a 1 indicates a command in progress.

Mark type: For FD179x a 0 indicates a normal data mark (>FB),a 1 indicates a deleted data mark (>F8). For FD1771, two bits areused:00 = >FB, 01 = >FA, 10 = >F9, 11 = >F8.

Write fault: a 1 indicates a write fault detected by the drive.Reset when updated.

Rec not found: a 1 indicates the desired track+sector+side IDcombinationwas not found in any ID block.

Lost data: a 1 indicates that the CPU did not read/write thedataregister in time for the next byte to be processed.

DRQ pin: copy of the DRQ pin. For read operations, a 1 indicatesthat the Data register is full and must be read. For write operations,a 1 indicates that the Data register is empty and must be filled. Resetwhen updated.

Step

This command causes the FDC to issue a pulse on the STEP pin, whichresults in moving the magnetic head by one track in the currentlyselecteddirection. If the h flag is set, the head will be loaded onto themagneticmedium at the beginning of the command. After a delay specified by ther0+r1 bits, the track number is verified from the first encountered IDfield, provided the V flag was set (no verification is done with theFD1795/97).Finally, if the T flag is set, the Track register will beincremented/decrementedby one.

Head step times (the usual value for the TIcontroller card is in bold)

| Clock | 2 MHz | 2 MHz | 1 MHz | 1 MHz | 2 MHz | 1 MHz | 2MHz | 1 MHz | 2MHz | 1MHz | |

|---|---|---|---|---|---|---|---|---|---|---|---|

| DDEN* | low | high | low | high | any | any | FD1771 | FD1771 | FD1771 | FD1771 | |

| TEST* r1 r0 | high | high | high | high | low | low | high | high | low | low | |

| 0 | 0 | 3 ms | 3 ms | 6 ms | 6 ms | 184 us | 368 us | 6 ms | 12 ms | ~400 us | ~600 us |

| 0 | 1 | 6 ms | 6 ms | 12 ms | 12 ms | 190 us | 380 us | 6 ms | 12 ms | ~400 us | ~600 us |

| 1 | 0 | 10 ms | 10 ms | 20 ms | 20 ms | 198 us | 396 us | 10 ms | 20 ms | ~400 us | ~600 us |

| 1 | 1 | 15 ms | 15 ms | 30 ms | 30 ms | 208 us | 416 us | 20 ms | 40 ms | ~400 us | ~600 us |

NB The CorComp card provides a way to determine the proper head-steptime by reading CRU bits 18 and 22. You can determine which card is inuse by trying to bank-switch the card ROM with CRU bit 11: if the ROMchanges,it's probably a CorComp card. Don't forget that it does not invert thedata bus!

Step-in

This commands sets the current direction as 'inward' (pinDIRC is high), then executes a Step command.

Step-out

This commands sets the current direction as 'outward' (pinDIRC is low), then executes a Step command.

Seek

The CPU uses this command to move the magnetic head on a specifictrack.The desired track number should be loaded in the Data register and itisassumed that the Track register contains an up-to-date track number.Thelatter can be a problem when using multiple drives: the current tracknumberfor a drive must be saved by the software before to operate anotherdrive.Upon reception of the command, the FDC compares these two registers todetermine the adequate direction and sets the DIRC pin accordingly. Itthen executes the required number of Step commands to make the Trackregistermatch the Data register.

Restore

This command seeks track 0. It sets the Track register as 255 andtheData register as 0. Then is executes a Seek command, which will resultin moving the magnetic head outwards. The Restore command constantlymonitorsthe TR00* pin: when the head reaches track 0 this pin goes low and thecommand is aborted. The Track register is set as 0, and the tracknumberis verified (by reading an ID block) if the V flag was set. If TR00*doesnot become active after 255 steps, a Seek error is issued (provided theV flag was set) and the command terminates. This command isautomaticallyexecuted after a master reset.

Read sector

This commands reads one or more sectors from disk (only the datapartof the sector is transfered). The desired sector number should beplacedin the Sector register.

For obvious reasons, the FDC always activated the HLD pin to loadthemagnetic head at the beginning of a read or write command. Thisoperationtakes some time and there are two ways to wait for its completion.Beforeto perform any read/write operation, the FDC waits for the HLT pin tobecomeshigh, a feature meant for use with an external 'one-shot' timer.If the 'E' bit is set, the FDC first wait 15 msec (10 msec withthe FD1771) before to check the HLT pin, a feature meant for use with aHLT pin permanently tied to +5V.

If the content of the Track register is greater than 43, the TG43pinis set as high, otherwise it is set as low.

The Read sector command then checks every ID block on the currenttrackuntil it encouters one that matches the required parameters. It firstverifiesthat the track number matches the content of the Track register, thenthatthe sector number matches the content of the Sector register, then thatthe side number matches the 'S' bit in the Command register.If there is a mismatch the next ID block is checked. If no matching IDblock (or no ID block at all) is found whithin 5 disk revolutions, asdetectedby the index hole pulses on the IP* pin, the command ends with the 'recnot found' bit set in the Status register. If a matching ID blockis found, the FDC loads the sector size and check the CRC. If the CRCdoesnot match, the search continues.

When a matching ID field is found, the FDC expects a data markwithinthe next 30 bytes (43 for double-density disks). If none occured, thesearchprocedure resumes. Once the data mark has been found, the CRC counterisreset and bytes read from disk are transfered to the Data register, viathe shift register. Once a byte is ready, the DRQ pin is activated andthe CPU must read the Data register before the next byte arrives (whichresets the DRQ pin). If this did not happen, the ' lost data'bit is set in the status register, but reading continues normally.

Once the appropriate number of bytes have been read, the CRC fieldisread and compared with the calculated CRC value. If they don't match,thecommand aborts and sets the 'CRC error' bit in the Status register.Otherwise the commands terminates normally and the type of address markis saved in the 'mark type' bit of the status register.

If the m bit is set in the Command register, the FDC increments theSector register and proceeds with reading the next sector. This goes onuntil either a sector cannot be found on the track, or the Forceinterruptcommand is received.

Sector length coding.

The L flag exists only on the FD1795/97. It is assumed to be 1 ontheother models. For the FD1771, the L flag selects either the IBM set ofsizes (128, 256, 512 or 1024 bytes ) or a non-IBM set in which thesectorlength field is multiplied by 16 to yield the sector length (0 standsfor256, ie. 4096 bytes). The default value for the TI-99/4A controllercardis 256 bytes.

| L flag in command | Sector length in ID field | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 2 | 3 | ...n | >FF | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0: FD179x | 256 | 512 | 1024 | 128 | - | - | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Byte | Meaning in FM | Meaning in MFM |

|---|---|---|

| >00- >F4 | Written normally | Written normally |

| >F5 | Not allowed | Write >A1, missing clock between bits 4-5 Reset CRC |

| >F6 | Not allowed | Write >C2, missing clock between bits 3-4 |

| >F7 | Generate 2 CRC bytes | Generate 2 CRC bytes |

| >F8- >FB | Written as a mark with clock pattern >C7. Reset CRC | Written normally |

| >FC | Written as a track mark (clock >D7) | Written normally |

| >FD | Written normally. Reset CRC. | Written normally |

| >FE | Written as a mark with clock pattern >C7. Reset CRC | Written normally |

| >FF | Written normally | Written normally |

Force interrupt

This command is generally used to stop a multiple Sector read orSectorwrite. It can also be used to place the Status register in a definedstate:if a command is interrupted, the Status register reflects the currentstatusof this command (with the 'busy' bit cleared), otherwise themeaning of the status byte is that of the Force interrupt command.Finally,this command can be used to physically generate interrupts.

Interrupts are issued by setting one (or more) of the I0-I3 bits to1. When one of the conditions for the interrupt is met, the INTREQ linegoes active (high). I3 issues an interrupt immediately. I2 issues aninterruptwhen an index hole is detected. I1 and I0 issue interrupts when theREADYpin changes state: I1 when it becomes not-ready, I0 when it becomesready.I0 to I2 are reset automatically, but I3 must be reset by loadinganotherForce interrupt command, with I3=0.

The CPU should wait 8 usec (16 usec for DD) after the command isloaded,before loading another command (else it would cancel the Forceinterrupt).These times doubble with a 1 MHz clock.

Timing diagrams

When diagrams are valid for both the FD1771 and the FD179x, valuesspecificfor the FD179x are indicated in green.Alltimes are for a 2 MHz clock, you should double them for a 1MHz clock.

CPU interface: Read enable

CPU interface: Write enable

FD1771 drive interface: Input data with separator

Without separator

FD1771 drive interface: Write data

FD179x drive interface: Input data

FD179x drive interface: Write data

Drive interface: Stepping

Drive interface: Other signals

Electrical characteristics

Absolute maximum ratings

For the FD1771

Vdd to Vss.....................+20V to -0.3V

Any input to Vss.............+20V to -0.3V

Icc.................................30 mA nominal

Idd................................10 mA nominal

Ibb................................0.4 uA nominal

Operating temp..............0 to 70 `C

Storage temp................-55 to +125 `C

For the FD179x

Vdd to Vss.....................+15V to -0.3V

Any input to Vss.............+15V to -0.3V

Icc.................................60 mA (35 mA nominal)

Idd................................15 mA (10 mA nominal)

Cin................................15 pF max

Cout..............................15 pF max

Operating temp..............0 to 70 `C

Storage temp................-55 to +125 `C

Operating characteristics

FD1771: Vdd = +12V, Vss = 0V, Vcc = +5V, Vbb=-5V, TA = 0-70 `C

FD179x: Vdd = +6V, Vss = 0V, Vcc = +5V, TA = 0-70 `C

| Parameter | Test conditions | Min | Max | Unit |

|---|---|---|---|---|

| Input leakage | Vin=Vdd. Pins without pull-ups (not for pins 22,23,33,36,37) | . | 10 | uA |

| Output leakage | Vout=Vdd | . | 10 | uA |

| Input high voltage | . | 2.6 | . | V |

| Input low voltage | . | . | 0.8 | V |

| Output high voltage | I = -100 uA | 2.8 | . | V |

| Output low voltage | I = 1.6 mA (1.0 for 1792/94) | . | 0.45 | V |

| Power dissipation | . | . | 0.6 | W |

Next page

Revision 1. 5/15/99. OK to release (fully disassembled card ROM).

Revision 2. 5/30/99. Tested & debugged examples.Revision 3. 7/4/99. Added an explanation of the CRC.

Revision 4. 7/13/99. Added a paragraph on magnetic media and writeprecomp.

Revision 5. 9/18/99. Added data on the FD1771, a word on the CorCompcard.

Revision 6. 6/16/00. Got the FD171 manual. Added section on drives.Splitin two pages.

Revision 7. 4/14/05. Cluster offset in FDR description is zero-based.

Revision 7. 4/14/05. Cluster offset in FDR description is zero-based.